# WATERS 2016

Toulouse, France July 5<sup>th</sup>, 2016

http://waters2016.inria.fr

# Keynote, Rob Davis

On the Evaluation of Schedulability Tests for Real-Time Scheduling Algorithms

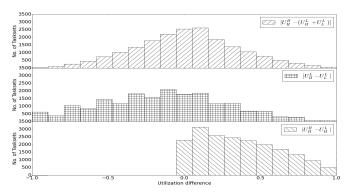

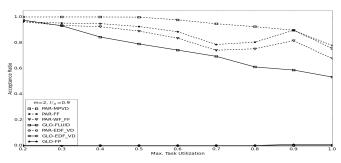

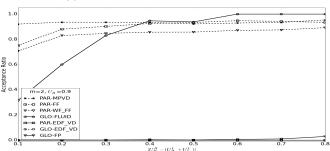

This talk discusses criteria and methods that can be used to evaluate the performance of schedulability tests for real-time scheduling algorithms. We briefly review theoretical methods such as utilisation bounds, dominance relations, and speed-up factors, as well as empirical methods such as simulation and case studies. The talk then focusses on empirical evaluation and the generation of parameters for synthetic task sets. We discuss the need for a systematic approach, issues of bias, confounding variables and statistical confidence. A simple evaluation framework is outlined, covering how to generate task utilisation values, periods and other parameters, as well as how task set parameters can be grounded in data from benchmarks. A simple systematic approach to covering the parameter space is proposed, and different ways of presenting results considered. Finally, the talk ends with an open discussion of the benefits of having a de-facto standard approach, and how we might improve the quality of empirical evaluation in the real-time community.

# **Regular Contributions**

Code Generation of Time Critical Synchronous Programs on the Kalray MPPA Many-Core architecture *Amaury Graillat*

MECHAniSer – A Timing Analysis and Synthesis Tool for Multi-Rate Effect Chains with Job-Level Dependencies *Matthias Becker, Dakshina Dasari, Saad Mubeen, Moris Behnam and Thomas Nolte*

A Simulation Framework to Analyze the Scheduling of AVR tasks with respect to Engine Performance *Paolo Pazzaglia, Alessandro Biondi, Giorgio Buttazzo and Marco Di Natale*

Model Interpretation for an AUTOSAR compliant Engine Control Function Sakthivel Manikandan Sundharam, Sebastian Altmeyer and Nicolas Navet

Evaluation of Mixed-Criticality Scheduling Algorithms using a Fair Taskset Generator *Saravanan Ramanathan and Arvind Easwaran*

Dynamic criticality management with ARTEMIS Olivier Cros, Geoffrey Ehrmann and Laurent George

NTGEN: a Network-on-Chip Traffic Generator toolkit for latency analysis *Ermis Papastefanakis, Laurent George, Xiaoting Li and Ken Defossez*

# **Verification Challenge**

Calculating Latencies in an Engine Management System Using Response Time Analysis with MAST Juan M Rivas, J. Javier Gutiérrez, Julio Medina and Michael González Harbour

A Novel Analytical Technique for Timing Analysis of FMTV 2016 Verification Challenge Benchmark *Junchul Choi, Donghyun Kang and Soonhoi Ha*

FMTV 2016: Where is the Actual Challenge? *Alessio Balsini, Alessandra Melani, Pasquale Buonocunto and Marco Di Natale*

Computational Analysis of Complex Real-Time Systems – FMTV 2016 Verification Challenge *Ingo Stierand, Philipp Reinkemeier, Sebastian Gerwinn and Thomas Peikenkamp*

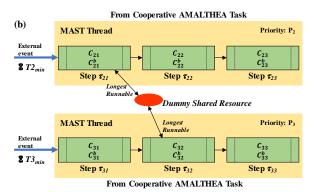

Schedulability and Timing Analysis of Mixed Preemptive-Cooperative Tasks on a Partitioned Multi-Core System *Ignacio Sanudo, Paolo Burgio and Marko Bertogna*

# Regular Contributions

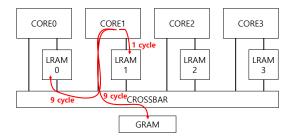

# Abstract: Code Generation of Time Critical Synchronous Programs on the Kalray MPPA Many-Core architecture

Embedded software as found in aircraft, nuclear power plants and cars, is said to be critical since bugs can have hazardous consequence to human lives. A bug can be behavioral or temporal for instance a result too late is a bad result. Hence, we talk about time-critical software. The Worst-Case Response Time is the bound of this result computation. Critical codes are often generated from formal languages such as the Dataflow Synchronous Languages (SCADE, Lustre, Esterel, etc). Today the critical systems are still running on old single-core processors since theses processors are quite simple and make the computation of the WCRT easy. But, the growing demand for computational power in avionics and automotive makes the single-core processors limited. Multi-core processors offer enough computational power but are often too complex to allow computation of the WCRT. Hence, many-core processors are promising because they offer high computational power thanks to numerous but very simple cores.

Our purpose is to parallelize and implement a Dataflow Synchronous program written in SCADE on a many-core processor. Nodes are statically scheduled on the cores to enhance temporal predictability. As the communications are in shared-memory, the solution makes the interferences as predicable as possible to allow the computation of the WCRT.

We use a prototype of the SCADE compiler that allows developer to specify the nodes of the program that must be executed in parallel. With this information, the compiler generates new blocks that communicate through data channels. A channel is composed of a data structure containing the data transferred between the blocks and special macros to write and read in this structure.

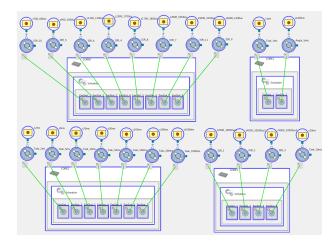

The execution platform is composed of 16 cores and a shared-memory divided into 16 banks such that access on a bank has no interference on the timing of access of another bank. According to the mapping information given by the developer, a node is executed on a core and its code stored in the corresponding memory bank. A sequencer allows several nodes to be executed sequentially one a core. Channels are implemented in a Remote Write manner, *i.e.*, the result of a node in written in the memory banks of the destination nodes. To make the interference prediction easier for each node, two releases are defined: a release for execution, and a release to write the result.

We have implemented a code generator for the Kalray MPPA Bostan many-core SoC that takes the output of the SCADE compiler and the mapping and timing information provided by the developer, to generate C code using the Kalray low level libraries.

We applied our study to ROSACE, an open source case-study of a flight controller. It is composed of an altitude controller and an environment simulator. We parallelized the altitude controller on one cluster using 5 cores. The environment simulation was located on a second cluster communicating through the network-on-chip.

# MECHAniSer - A Timing Analysis and Synthesis Tool for Multi-Rate Effect Chains with Job-Level Dependencies

Matthias Becker\*, Dakshina Dasari<sup>†</sup>, Saad Mubeen\*, Moris Behnam\*, Thomas Nolte\*

\*MRTC / Mälardalen University, Sweden {matthias.becker, saad.mubeen, moris.behnam, thomas.nolte}@mdh.se

<sup>†</sup> Research and Technology Centre, Robert Bosch, India dakshina.dasari@in.bosch.com

Abstract—Many industrial embedded systems have timing constraints on the data propagation through a chain of independent tasks. These tasks can execute at different periods which leads to under and oversampling of data. In such situations, understanding and validating the temporal correctness of end-to-end delays is not trivial. Many industrial areas further face distributed development where different functionalities are integrated on the same platform after the development process. The large effect of scheduling decisions on the end-to-end delays can lead to expensive redesigns of software parts due to the lack of analysis at early design stages. Job-level dependencies is one solution for this challenge and means of scheduling such systems are available. In this paper we present MECHAniSer, a tool targeting the early analysis of end-to-end delays in multi-rate cause effect chains with specified job-level dependencies. The tool further provides the possibility to synthesize job-level dependencies for a set of cause-effect chains in a way such that all end-to-end requirements are met. The usability and applicability of the tool to industrial problems is demonstrated via a case study.

### I. INTRODUCTION

Many application domains for embedded systems are subject to timing constraints in order to fulfill their requirements. Such real-time systems are well studied and several tools are available to analyze these properties. However, for many systems it is not only important that the individual tasks execute within their specified deadlines, but also that data propagates through a chain of tasks within a specified end-to-end delay constraint. In the automotive industry such chains are called cause-effect chains [1], [2]. The tasks in such a chain can have different activation periods which makes the calculation of such end-to-end delays a challenging task since over and undersampling effects need to be considered.

Currently it is left to the discretion of the system designer to guarantee that all end-to-end delay constraints are met in the system. While this is viable in small applications, the growing complexity of industrial applications renders this approach increasingly difficult. Automotive applications for example contain several multi-rate cause-effect chains [3]. Additionally, one task can be part of several chains which increases the problem complexity further.

This highlights the need for tool support during the system design, giving the designer viable input during early stages of the development where only limited or even no concrete knowledge of the schedule is present. This need is further increased since applications of several suppliers may be integrated on the same Electronic Control Unit (ECU) during

the system integration which is usually done by the Original Equipment Manufacturer (OEM). Changes in the system design can be very expensive at this stage. Having means to obtain end-to-end delay bounds for the data propagation through a chain of tasks before the system integration can thus provide valuable information and reduce the risk of costly design changes in the later development phases.

One way to reduce the possible data propagation among tasks of different rate is the use of job-level dependencies [4]. A job-level dependency introduces a constraint in the data propagation between two tasks and is specified on job-level. Several works address the scheduling problem of systems with specified job-level dependencies. These works cover fixed-priority and dynamic priority scheduled systems [5], [6], as well as time triggered schedules [7], [8]. The problem of analyzing such systems and to synthesize job-level dependencies is addressed in [9].

## A. Contributions

Several available tools support the end-to-end delay analysis of cause-effect chains, which are primarily based on the principles proposed in [10]. They however assume that knowledge of the task schedule is available when the system is analyzed. In contrast, the proposed tool MECHAniSer can be helpful in the early design phases where the exact task schedule is unknown. Its key features include analysis to i) compute bounds on the end-to-end delays ii) synthesize job-level dependencies when specified timing constraints are violated iii) compute end-to-end analysis in the systems where job-level dependencies are specified. To facilitate a faster system design, the tool implements a heuristic to place job-level dependencies in a system consisting of several, possibly interconnected, cause-effect chains. This is done in a way such that the maximum data age delay of each cause-effect chain is met.

# B. Paper Layout

The rest of the paper is organized as follows, in Section II the system architecture and background information is provided. In Section III the calculations to obtain the data age delay are described before the tool itself is discussed in Section IV. The tool is evaluated based on a case study in Section V, followed by a discussion of related tools in Section VI and the conclusions and future work in Section VII.

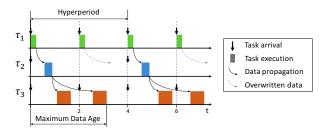

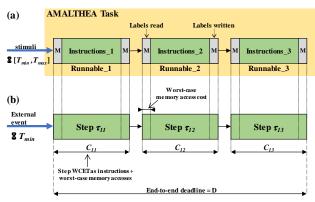

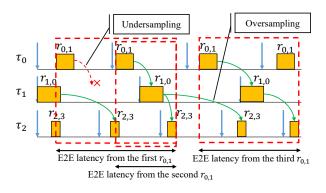

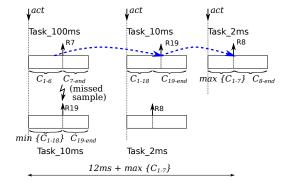

Fig. 1: Data propagation between tasks of a cause-effect chain in a real-time system with maximum data age specified.

### II. SYSTEM ARCHITECTURE AND BACKGROUND

### A. System Model

The system is comprised of a set of periodic tasks  $\Gamma$ . Each task  $\tau_i \in \Gamma$  can be described by the tuple  $\{C_i, T_i\}$ , where  $C_i$  is the task's Worst Case Execution Time (WCET), and  $T_i$  is the task's period. All tasks have implicit deadlines, i.e. the deadline of  $\tau_i$  is equal to  $T_i$ . For all tasks executing on a processor, the hyperperiod can be defined as the least common multiple of all periods,  $HP = \text{LCM}(\forall T_i, i \in \Gamma)$ . Hence, a task  $\tau_i$  executes a number of jobs during one HP, where its  $j^{th}$  job is denoted by  $\tau_{i,j}$ .

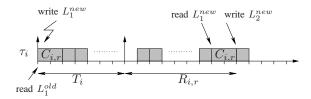

# B. Communication Model

In this work inter task communication is realized via shared registers, a model commonly used in the industrial domain [10], [11]. With this, a sending task writes an output value to a shared register, which is then read by the receiving task without the need for any signaling between the communicating tasks. Also, the receiving task always consumes the newest value present in the shared register.

In order to facilitate determinism, a *read-execute-write* semantic is followed in which a task reads all its input values into *local copies* before the execution starts. It then executes by acting on these local copies and writes the output values after the execution back to the shared registers, making them available to other tasks. In short, reading and writing of input and output values is done at deterministic points in time, i.e. at the beginning and end of the tasks execution respectively. This is a common communication mechanism found in several industrial standards (i.e. in AUTOSAR this model is defined as *implicit communication* [12], the standard IEC 61131-3 for automation systems defines similar communication mechanisms [13]).

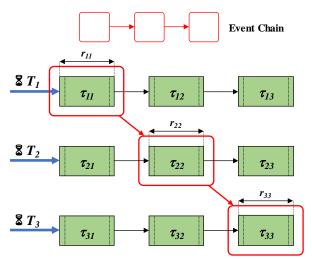

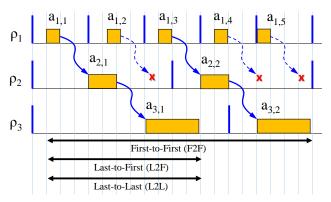

# C. End-to-End Timing Requirements

A cause-effect chain is typically specified by an end-toend timing requirement, as defined for automotive systems in [1], [2]. In this work the *data age*, the most important timing requirement in control systems, is examined. A detailed discussion of corresponding end-to-end delays is provided in [10]. For data age, the maximum time from sampling an initial input value at the beginning of the cause-effect chain, until the last time this value has influence on the produced output of the cause-effect chain is of interest. Fig. 1 depicts an example with three tasks,  $\tau_1$ ,  $\tau_2$ , and  $\tau_3$ . All tasks are part of a cause-effect chain in this order. Note that  $\tau_1$  and  $\tau_3$  are

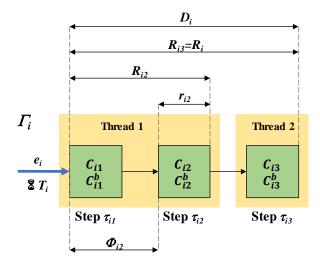

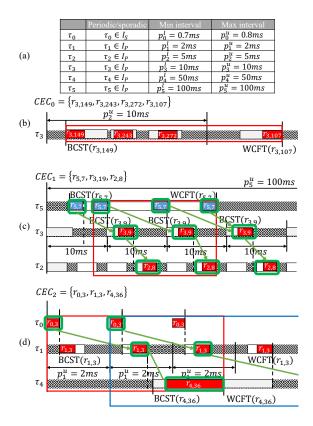

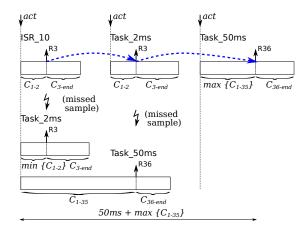

Fig. 2: Read and data intervals of consecutive jobs of  $\tau_i$  if no scheduling information is available.

activated with a period of T=2, while  $\tau_2$  is activated with a period of T=4. This leads to over- and under-sampling between the different tasks. While the output value of the first instance of  $\tau_1$  is consumed by the first instance of  $\tau_2$ , the data produced by the second instance of  $\tau_1$  is overwritten before  $\tau_2$  has the chance to consume it. Similarly, data produced by the first instance of  $\tau_3$ . Since no new data is produced before the second instance of  $\tau_3$  is scheduled the same data is consumed by  $\tau_3$  again. In the example, this constitutes the maximum data age, from sampling of the first instance of  $\tau_1$  until the last appearance of the data at the output of the second instance of  $\tau_3$ .

# D. Job-Level Dependency

A job-level dependency is similar to the rate transition operator of PRELUDE [4]. Defined between two tasks, a job-level dependency specifies which job of a task needs to finish its execution before a certain job of the successor task can start.

A job level dependency is described as  $\tau_i \xrightarrow{(k,l)} \tau_j$ , meaning that the  $k^{th}$  job of  $\tau_i$  needs to proceed the  $l^{th}$  job of  $\tau_j$ . This also implies that the dependency between the two jobs applies for the duration of the hyperperiod of the two jobs only, e.g.  $LCM(\tau_i,\tau_j)$ .

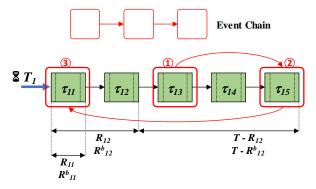

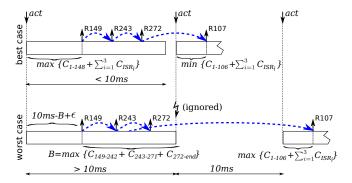

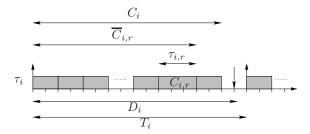

# III. CALCULATING LATENCIES

In this section, we recapitulate the calculation of data propagation paths for systems without prior knowledge of the schedule. For a more in depth explanation a reader is referred to [9]. Several properties of tasks under register communication are observed to determine reachability between jobs. Based on this the different data propagation paths of the cause-effect chain can be calculated.

## A. Reachability between Jobs

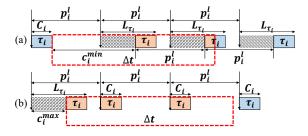

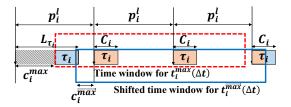

The concepts of *read interval* and *data interval* are central to decide if data can be propagated between two distinct jobs. For a job  $\tau_{i,j}$ , the read interval is defined as the interval starting from the earliest time  $\tau_{i,j}$  can potentially read its input data  $(R_{min}(\tau_{i,j}))$  until the last possible time  $\tau_{i,j}$  can do so without violating its timing constraints  $(R_{max}(\tau_{i,j}))$ . Similarly, the data interval is defined as the interval from the earliest time the output data of  $\tau_{i,j}$  can be available  $(D_{min}(\tau_{i,j}))$  up to the latest time a predecessor job of the same task overwrites the data  $(D_{min}(\tau_{i,j}))$ . Hence, the read interval  $RI_{i,j}$  is the interval  $[R_{min}(\tau_{i,j}), R_{max}(\tau_{i,j})]$ , and the data interval is  $[D_{min}(\tau_{i,j}), D_{max}(\tau_{i,j}))$ . These concepts are depicted in Fig. 2 for jobs of a task  $\tau_i$ . For a system without any knowledge of the scheduling decisions, one has to assume that a job can be scheduled anywhere, as long as it starts not

Add Task

Name: ActPed

Period: 5 ms

WCET: 1 ms

Size: 150 byte

(a) Window to add a task.

(b) Window to add a dependency.

Fig. 4: Windows to add new elements.

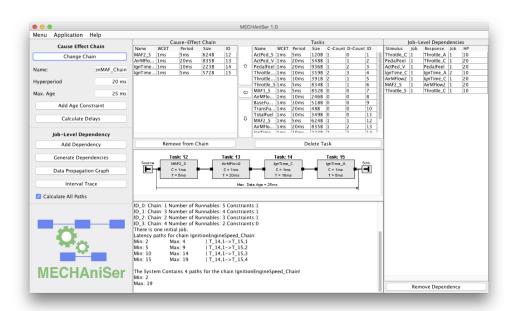

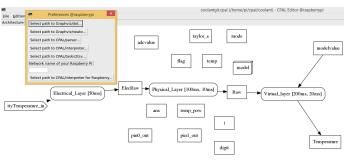

Fig. 3: Main view of the tool.

before its release and finishes not after its deadline. In [9], the notations to define the intervals are as follows:

$$R_{min}(\tau_{i,j}) = (j-1) \cdot T_i$$

$$R_{max}(\tau_{i,j}) = R_{min}(\tau_{i,j+1}) - C_i$$

$$D_{min}(\tau_{i,j}) = R_{min}(\tau_{i,j}) + C_i$$

$$D_{max}(\tau_{i,j}) = R_{max}(\tau_{i,j+1}) + C_i$$

1) Deciding Reachability between Jobs: In order for a job  $\tau_{k,l}$  to consume data of a job  $\tau_{i,j}$  the data interval of  $\tau_{i,j}$  must intersect with the read interval of  $\tau_{k,l}$ . The function Follows $(\tau_{i,j}, \tau_{k,l})$  is defined to return true if this is the case:

$$Follows(\tau_{i,j}, \tau_{k,l}) = \begin{cases} true, & \text{if } RI_{i,j} \cap DI_{i,j} \neq \emptyset \\ false, & \text{otherwise} \end{cases}$$

2) Adjusting the Data Interval for Long Chains: In order to capture the characteristics of data propagation in a cause-effect chain of length > 2, the data interval needs to be modified. Assume the first job of  $\tau_i$ , as shown in Fig. 2 is followed by a job of a task  $\tau_k$ .  $\tau_k$  is released with same period as  $\tau_i$ , but its execution time is shorter than the one of  $\tau_k$ . Follows $(\tau_{i,1},\tau_{k,1})$  returns true and indicates that  $\tau_{i,1}$  can potentially consume the data of  $\tau_{k,1}$ . However, in order to decide reachability between the  $\tau_{k,1}$  and a third task in the chain the data interval of  $\tau_{k,1}$  must be modified. This is the case because  $\tau_{k,1}$  can consume the data of  $\tau_{i,j}$  earliest at time  $D_{min}(\tau_{i,j})$ . Consequently, this data can earliest be available as output data of  $\tau_{k,l}$  at time  $D_{min}(\tau_{i,j}) + C_k$ .  $D'_{min}(\tau_{k,l},\tau_{i,j})$  defines the starting time of the data interval of  $\tau_{k,l}$  if the data produced by  $\tau_{i,j}$  shall be considered as well:

$$D'_{min}(\tau_{k,l}, \tau_{i,j}) = \max(D_{min}(\tau_{i,j}) + C_k, D_{min}(\tau_{k,l}))$$

Note that the data interval only needs to be adjusted if  $D_{min}(\tau_{k,l})$  is smaller than  $D_{min}(\tau_{i,j}) + C_k$ . These modifications are local for the specific data path, hence, if another

combination of jobs is involved the original data interval must be used.

# B. Calculating Data Paths

To calculate all possible data propagation paths in a system, a recursive function is used. This function constructs all possible data propagation paths from a job of the first node in a cause-effect chain up to the job of a last node of the chain. Consequently this needs to be done for all jobs of the first task of a chain, inside the hyperperiod of the chain.

As a result a set of data propagation paths is provided, where each path comprises an ordered list of involved jobs.

C. Constructing Data Propagation Paths and Max. Data Age

For a given data path, the maximum end-to-end latency and the data age, is computed. Given  $\tau_{start}$  is a job of the first task of the cause-effect chain, and  $\tau_{stop}$  is a job of the last task of a cause-effect chain:

$$AgeMax(\tau_{start}, \tau_{end}) = (R_{max}(\tau_{end}) + C_{\tau_{end}}) - R_{min}(\tau_{start})$$

In order to compute the maximum data age for any possible path in the system, AgeMax() must be computed for all data paths. The maximum of these values is the maximum data age of the cause-effect chain.

### IV. TOOL LAYOUT AND USAGE

This section briefly outlines the different forms of data input to the tool. Further the tool layout and its usage are discussed and a closer look is provided into the different visualization options.

# A. Input Formats

The tool specifies its own XML format to save a current project. Additionally it is possible to import projects designed with AMALTHEA V1.0[14]. AMALTHEA is an open tool platform for the design of multi-core systems in the automotive domain. The implementations for the support of additional

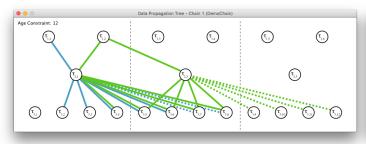

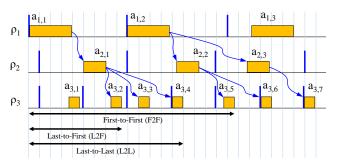

(a) The graph view in MECHAniSer. Edges between nodes depict possible data propagation while dashed edges show paths leading to larger data age then specified with the age constraint. The same chain with generated job-level dependencies is shown in the right window.

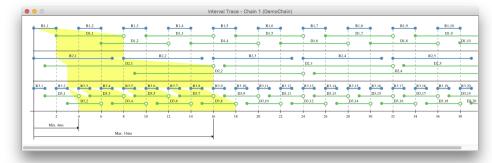

(b) The trace-view of MECHAniSer depicts the read- and data-interval of each involved job and visualizes the minimum and maximum data age of initial jobs as well as their possible data propagation range (in yellow).

Fig. 5: The two different visualization options for a cause-effect chain.

tools (i.e., AMALTHEA V1.1, Rubus ICE [15]) are currently ongoing and will be made available in the future.

# B. Layout and Usage

The tool is built around a main panel which is shown in Fig 3. The panel depicts the chain under analyis and also provides clickable interfaces to additional features of the tool.

1) The Main Panel and its Parts: The main window displays information about all tasks of the system, in the "Tasks"-table, as well as on all specified job-level dependencies in the "Job-Level Dependency"-table. The selected chain is graphically visualized, as shown in Fig. 3, while the "Cause-Effect Chain"-table describes the different parameters of the chain. This chain can further be analyzed and modified. The left column also provides means to manage job-level dependencies. The additional views can also be opened here via the button "Data Propagation Graph" and "Trace View". Output for the user is provided in the text-box at the bottom part of the window.

A user can add or delete a task over the "Application"-menu (see Fig. 4a) with the "Add Task" and "Delete Task" buttons. Note that the tool also displays the number of chains and the number of job-level dependencies that a task is part of. In order to keep the system consistent, a task must first be removed from all cause-effect chains and from all job-level dependencies before it can be removed from the system.

The chain which needs to be analyzed is selected via the button "Change Chain". This action pops up a window wherein a user can select the desired cause-effect chain. Once approved, the tool updates the related views. A new task can be added to the chain by selecting the respective task in the task table and then clicking the left-arrow button which appends the task to the chain. The correct position of a task is set by selecting the task in the chain table and then clicking the upand down-button which alter the tasks position. A task can be removed from the chain by selecting the task followed by the button "Remove from Chain".

Finally a maximum data age constraint can be specified on the chain by clicking on the button "Add Age Constraint". This pops up a window where the age constraint can be specified. Note that this new input overwrites any previously specified constraint. A constraint can be removed by specifying a maximum data age of 0.

2) Calculating Minimum and Maximum Data Age: The minimum and maximum data age of the currently selected cause-effect chain under consideration of all specified joblevel dependencies can be computed by clicking on the button "Calculate Delays". This action computes delays by applying the analysis presented in [9]. All data propagation paths are calculated, implying all possible paths that the data can propagate, when read from any of the initial jobs of the chain.

An initial job is defined as any job that the first task of the cause-effect chain releases during the first hyperperiod of the chain. Since the number of possible paths depends on the number of involved tasks as well as on the involved periods, a large number of data propagation paths might be generated. A user has hence the possibility to uncheck the option "Calculate All Paths" which will only calculate the data propagation path for the minimum and maximum job at each chain level. Hence this reduces the complexity of the calculation and simplifies the post processing by the system designer.

3) Adding and Synthesizing Job-Level Dependencies: The second strength of the tool is to handle job-level dependencies.

The left column of the main window provides means to add a job-level dependency manually as well as to synthesize job-level dependencies for all cause-effect chains in the system. The button "Add Dependency" opens a new window (see Fig. 4b) which allows to select the two involved tasks and the dependent instances. Note that first the two tasks need to be selected before the menu for the involved jobs becomes active. This is the case since, depending on the selected tasks, the available job instances change.

The button "Generate Dependencies" triggers a heuristic [9] which adds job-level dependencies to the system in a way that all specified age-constraints are met. Already specified dependencies are not affected. The main intuition behind the heuristic is that a placement of a job-level dependency can prune a branch of the data propagation tree. Hence the heuristic adds dependencies in a way such that all branches which lead to larger end-to-end delays than specified are removed.

- 4) The Graph View: The graph view, as shown in Fig. 5a, depicts the data propagation tree of the currently selected chain. Each data path originating from the different initial nodes is colored differently for a more effective visual presentation. The different jobs of the involved tasks are drawn in a way that the data always propagates from top to bottom, i.e. the beginning of the chain is at the top and the last task of the chain is at the bottom. Branches which lead to end-to-end delays larger than the specified constraint are shown in dashed lines. These branches need to be removed in order to meet the specified constraints. Note that this representation depicts no time information, the execution of the jobs depends on the exact path a data propagates and hence cannot be shown in this overview. However, jobs are grouped such that jobs of the same hyperperiod are arranged together and separated by the vertical dashed lines. A user can obtain further information of the different nodes by clicking on them which then displays an information box.

- 5) The Trace View: The trace view is shown in Fig. 5b. This view visualizes the read- and data-interval of all jobs of one chain (see Fig. 2 for a description). Initially the first initial job is selected and the propagation of the calculated data paths is visualized via yellow overlay. Additionally the minimum and maximum data age of these data paths are shown. A user can change this view to any other initial job by clicking on the respective read interval.

### C. Implementation and Distribution

To be platform independent, the tool is developed in Java. The main development is performed under OSX which might cause a diverging visual appearance on other platforms. The tool is freely available online<sup>1</sup>. A user documentation and examples are provided under the same link.

# V. CASE STUDY

The applicability of the presented tool is demonstrated on a case study of an Engine Management System (EMS). This case study is adapted from the results presented in [11]. The EMS consists of several subsystems which control the air

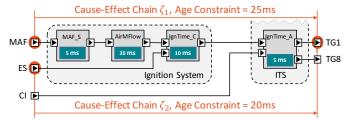

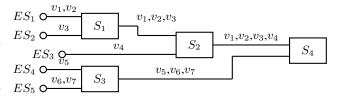

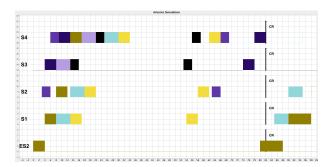

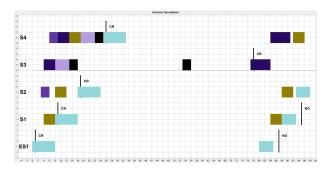

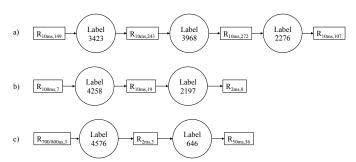

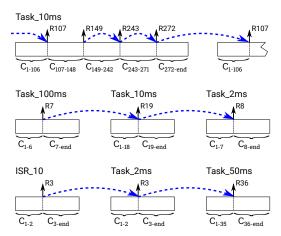

Fig. 6: Tasks and specified cause-effect chains of the IS and ITS.

and gas mixture which is injected into the cylinders. The Air Intake System (AIS) controls the amount of air via the throttle position, while the Fueling System (FS) controls the amount of gas which is injected per stroke. The Ignition System (IS) controls the exact time of the ignition, both FS and IS feed into the Injection Time and Ignition Time Actuation System (ITS). For a smooth and energy efficient operation of the vehicle, several age constraints must be met. The complete EMS of this case study comprises 16 different tasks which three different periods (5 ms, 10 ms, and 20 ms)

Due to space limitations, we discuss only part of the complete EMS. The case study includes two cause-effect chains,  $\zeta_1$ , and  $\zeta_2$ , which are specified from the Mass Air Flow (MAF) input to the output for Ignition Time of cylinder 1 to 8 (TG1-8). The cause-effect chain  $\zeta_2$  is specified from the Engine Speed (ES) input up to TG1-8. Both chains span from the IS to the output of the ITS. 4 tasks with 3 different periods are involved (see Fig. 6) and WCETs of all tasks are set to 1 ms. We refer to [9] for a case study of the AIS.

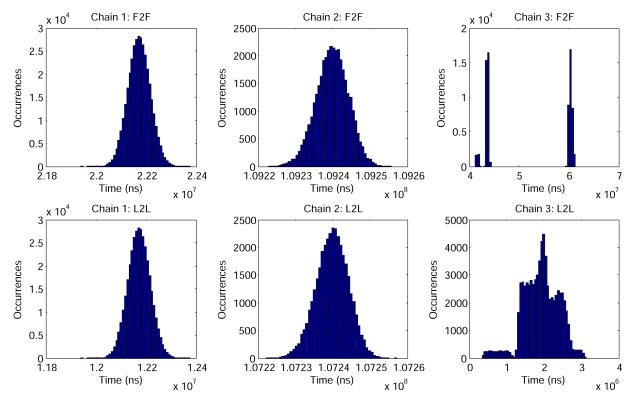

### A. Analysis of Latencies using MECHAniSer

Both specified cause-effect chains contain a number of runnables which are triggered at different periods. For the chain  $\zeta_1$  all four tasks are involved. The calculation of all data propagation paths results in 70 different paths, a minimum data age of 4 ms, and a maximum data age of 55 ms. The maximum possible data age exceeds the specified age constraint of 25 ms and the chain is not directly schedulable by the system. In the next step we will show how the tool generates job-level dependencies to remove the data propagation paths which exceed the constraint.

The second chain  $\zeta_2$  consists only of two tasks. Hence, the number of data propagation paths is smaller. Four paths are identified, with a minimum data age of  $2\,\mathrm{ms}$  and a maximum data age of  $20\,\mathrm{ms}$ . Here the specified age constraint of  $20\,\mathrm{ms}$  is met without the need to specify job-level dependencies.

The required computation time for the analysis of the two chains is  $5 \, \mathrm{ms}$  and  $2 \, \mathrm{ms}$  for  $\zeta_1$  and  $\zeta_2$  respectively.

### B. Synthesizing Job-Level Dependencies

The initial analysis of the two cause-effect chains revealed that, while  $\zeta_2$  meets its age constraint,  $\zeta_1$  does not. Hence job-level dependencies need to be generated in order to meet the constraint.

The tool generated three different job level dependencies in order to meet the constraint of the cause-effect chain. One job-level dependency was generated between each consecutive pair of tasks. This successfully reduces the maximum data age to 25 ms, allowing the cause-effect chain to meet its constraint.

<sup>&</sup>lt;sup>1</sup>http://www.mechaniser.com

The presence of the job-level dependencies further reduces the number of data propagation paths to 13. The required computation time is 19 ms. Since  $\zeta_2$  is subset of  $\zeta_1$ , the specified job-level dependency between the last two tasks of the cause-effect chain can have influence on  $\zeta_2$ , hence  $\zeta_2$  needs to be revalidated as well. The job-level dependency specified for the two tasks is defined between the first job of task  $IgnTime\_C$  to the second job of task  $IgnTime\_A$ , the parameters are not influenced and the latency stays at  $20 \, \mathrm{ms}$  with 4 different data propagation paths.

## VI. RELATED TOOLS

Many industrial standards specify constraints for the propagation of data through a chain of tasks [1], [2]. A detailed discussion of end-to-end delays is provided in [10]. The authors formally specify age- and reaction delays in multirate systems which communicate via register-communication and further develop a method to calculate end-to-end delays in such systems.

Several commercially available tools support the analysis of end-to-end delays in cause-effect chains. Examples are SymTA/S TraceAnalyzer for ECUs [16], Rubus ICE [15], and Timing Architects Inspector [17].

To the best of our knowledge the analysis presented in [10] is implemented in these tools [18], [19]. EELAP [20] is an open source end-to-end analyzer for the ProCom [21] real-time component model. The tool is built on the analysis of [10]. All these tools however require an existing schedule in order to analyze the system. Hence, the calculation of end-to-end delays in early design phases is not supported.

Several works address systems where job-level dependencies are specified [5], [6], [7], [8]. The application model in these works is specified by the *prelude* language [4] which specifies the rate-transition operation. On task level this operation is equivalent to a job-level dependency. The prelude compiler is available [22] and can generate synchronized multi-task C-code which then can be executed by the supported target OS. To the best of our knowledge, no tool exists that can automatically generate job-level dependencies in order to meet the end-to-end timing constraints.

# VII. CONCLUSION AND FUTURE WORK

In this paper we presented MECHAniSer, the first tool for the analysis and synthesis of multi-rate cause-effect chains with specified job-level dependencies. The tool allows to analyze systems at early design phases, where detailed scheduling knowledge is not available. Further, the tool synthesizes joblevel dependencies for a set of cause-effect chains in a way that all their end-to-end timing constraints are met. This allows such systems to be scheduled on any platform which supports these concepts [5], [6], [7], [8].

The tool provides its own XML format to store the project configurations but it also provides the possibility to import projects from existing tools and hence eases the design process. Multiple graphical views are provided to support the system designer and to ease the understanding of the data propagation in multi-rate cause-effect chains. Several extensions to the tool are possible. One limitation of the current

implementation is the time granularity. Future versions of the tool will allow to specify time values in smaller granularity than ms. Besides data age, many industrial applications specify reaction constraints. Analysis for this type of constraint is currently not supported but will be part of future work.

### ACKNOWLEDGMENT

The work presented in this paper is supported by the Swedish Knowledge Foundation (KKS) through the projects PREMISE and DPAC; and the Swedish Foundation for Strategic Research (SSF) through the projects PRESS.

### REFERENCES

- [1] AUTOSAR Spec. of Timing Extensions, AUTOSAR Std. 4.2.2, 2014.

- [2] EAST-ADL Domain Model Specification, EAST-ADL Association Std. V2.1.12, 2014.

- [3] S. Kramer, D. Ziegenbein, and A. Hamann, "Real world automotive benchmarks for free," in 6th International Workshop on Analysis Tools and Methodologies for Embedded and Real-time Systems, 2015.

- [4] J. Forget, F. Boniol, D. Lesens, and C. Pagetti, "A real-time architecture design language for multi-rate embedded control systems," in ACM Symposium on Applied Computing, 2010, pp. 527–534.

- [5] J. Forget, F. Boniol, E. Grolleau, D. Lesens, and C. Pagetti, "Scheduling dependent periodic tasks without synchronization mechanisms," in 16th IEEE Real-Time and Embedded Technology and Applications Symposium, 2010, pp. 301–310.

- [6] C. Pagetti, J. Forget, F. Boniol, M. Cordovilla, and D. Lesens, "Multitask implementation of multi-periodic synchronous programs," *Discrete Event Dynamic Systems*, vol. 21, no. 3, pp. 307–338, 2011.

[7] W. Puffitsch, E. Noulard, and C. Pagetti, "Off-line mapping of multi-

- [7] W. Puffitsch, E. Noulard, and C. Pagetti, "Off-line mapping of multirate dependent task sets to many-core platforms," *Real-Time Systems*, vol. 51, no. 5, pp. 526–565, 2015.

- [8] —, "Mapping a multi-rate synchronous language to a many-core processor," in 19th IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS), 2013, pp. 293–302.

- [9] M. Becker, D. Dasari, S. Mubeen, M. Behnam, and T. Nolte, "Synthe-sizing job-level dependencies for automotive multi-rate effect chains," in *Proceedings of the 22th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA)*, [Online] http://www.es.mdh.se/publications/4368-, 2016.

- [10] N. Feiertag, K. Richter, J. Norlander, and J. Jonsson, "A compositional framework for end-to-end path delay calculation of automotive systems under different path semantics," in *Int. Workshop on Compositional Theory and Technology for Real-Time Embedded Systems*, 2008.

- [11] P. Frey, "Ulmer Informatik Berichte Nr 2010-03 Case Study: Engine Control Application," University Ulm, Tech. Rep., 2010.

- [12] AUTOSAR Specification of RTE, AUTOSAR Std. 4.2.2, 2014.

last visited 16.05.2016.

- [13] IEC 61131-3, International Electrotechnical Commission Std., 2003.

[14] AMALTHEA, "An Open Platform Project for Embedded Multicore Systems," [Online] http://www.amalthea-project.org/index.php/contact,

- [15] Arcticus Systems, "Rubus ICE," [Online] https://www.arcticus-systems.com/products/, last visited 16.05.2016.

- [16] Symtavision GmbH, "SymTA/S and TraceAnalyzer for ECUs," [Online] https://www.symtavision.com/products/ecu-timing/, last visited 16.05.2016.

- [17] Timing Architects, "Timing Architects Inspector," [Online] https://www.timing-architects.com/ta-tool-suite/inspector/, last visited 16.05.2016.

- [18] R. Henia, A. Hamann, M. Jersak, R. Racu, K. Richter, and R. Ernst, "System level performance analysis - the symta/s approach," *IEE Proceedings - Computers and Digital Techniques*, vol. 152, no. 2, pp. 148–166, 2005.

- [19] S. Mubeen, J. Mäki-Turja, and M. Sjödin, "Support for end-to-end response-time and delay analysis in the industrial tool suite: Issues, experiences and a case study," *Computer Science and Information Systems*, vol. 10, no. 1, 2013.

- [20] J. Kuncar, R. Inam, and M. Sjödin, "End-to-end latency analyzer for ProCom - EELAP," Tech. Rep. ISSN 1404-3041 ISRN MDH-MRTC-272/2013-1-SE, 2013.

- [21] R. Inam and M. Sjödin, "Implementing and evaluating communicationstrategies in the procom component technology," SIGBED Rev., vol. 9, no. 4, pp. 41–44, 2012.

- [22] Prelude, "programming critical real-time systems," [Online] http://www.lifl.fr/%7Eforget/prelude.html, last visited 16.05.2016.

# A Simulation Framework to Analyze the Scheduling of AVR tasks with respect to Engine Performance

Paolo Pazzaglia, Alessandro Biondi, Marco Di Natale and Giorgio Buttazzo Scuola Superiore Sant'Anna, Pisa, Italy

Email: {name.surname}@sssup.it

Abstract—We present a simulation framework, based on Simulink and an extension of the T-Res scheduling simulator tool to help provide a better characterization of the very popular problem of scheduling and analysis of Adaptive Variable Rate Tasks (AVR) in engine control. The purpose of the tool is to go beyond the simplistic model that assumes hard deadlines for all tasks and to study the impact of scheduling decisions with respect to the functional implementations of the control algorithms and the true performance of the engine.

### I. INTRODUCTION

The study of the schedulability conditions for engine control tasks (or adaptive variable rate - AVR) is gaining popularity in the real-time research community because of the novel nature of the problem and the special activation conditions that apply to some of the system tasks. These tasks are not periodic or sporadic, but are activated by the rotation of the engine crankshaft (a parameter of the physical controlled system). In addition, to compensate for the increased CPU load at high rotation speeds (and more frequent activation times), the code implementation of these tasks is defined in such a way that at given speed boundaries, the implementation is simplified and the execution time is reduced. A typical engine control application consists of time-driven periodic tasks with fixed periods, typically between a few milliseconds and 100 ms (see [1], page 152), and angular tasks triggered at specific crankshaft angles. The activation rate of such angular tasks hence varies with the engine speed (variable-rate tasks). For example, for engines where the speed varies from 500 to 6500 revolutions per minute (RPM), the interarrival times of the angular tasks range from about 10 to 120 ms (assuming a single activation per cycle).

With respect to the set of activation instants, the dependency from a physical phenomenon characterizes this problem as truly belonging to the class of problems in cyber-physical systems (CPS). However, in many papers the dependency of the timing and scheduling problem from the physics of the controlled system is restricted to the set of activation events and every other concern is hidden under the typical assumption of hard deadlines.

In reality, this problem (as many others) is representative of a class of control systems in which deadlines can be missed without catastrophic consequences, and the problem should actually be defined as a design optimization, where the objective is to select the controls implementations and the scheduling policy in such a way that a set of engine performance functions are optimized (including power, emissions, noise, pollution). These performance functions depend in complex ways from timing parameters, such as jitter and latency. Informally, the objective of the scheduler is not to miss too many deadlines or produce actuation signals that are too much delayed.

Formally, the problem is quite complex and extremely unlikely to be solved in a simple, closed analytical form or even with a general procedure for expressing the dependency of th performance from scheduling. This is the reason for the investigation of alternative approaches that are based on the simulation of the three system components in a joint environment:

- A model of the engine and the combustion process in it (the physical system or plant)

- A model of the engine controls

- A model of the task configuration and the scheduling

# II. OUR SIMULATION FRAMEWORK FOR THE ANALYSIS OF THE PERFORMANCE IMPACT OF SCHEDULING

Our cosimulation framework follows the principles of CPS system analysis. It is based on the popular Simulink toolset and leverages the T-Res cosimulation environment for the simulation of the task scheduling [2].

For the development of the engine model we leveraged information from several sources, including engine models for the steady state and event-based models as described in [1] and other empirical models found online.

The engine controls are currently extremely simple and only contain a simple analytical formula that computes the angle of injection and the injection time that is defined by a calibration table.

Finally, the T-Res simulation framework described in [2] is used for modeling the scheduling delays.

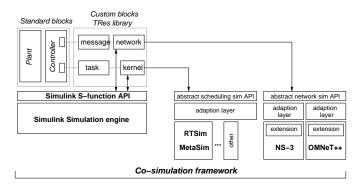

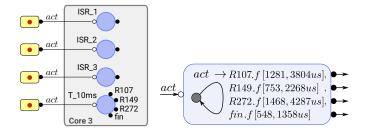

## III. EXTENDING T-RES FOR MODELING AVR TASKS

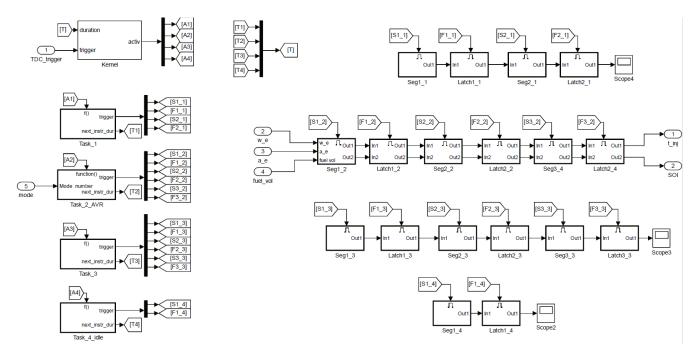

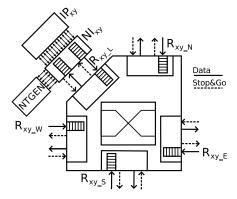

T-Res consists of a set of custom Simulink blocks representing tasks and kernels and allows to interface the Simulink simulation engine, acting as master, with a scheduling simulator in a co-simulation environment (see Figure 1). The scheduling simulator (we use RTSim [3], but the backend simulation engine can be changed) computes the scheduling delays and latches the outputs of the corresponding tasks until their simulated completion time. This allows to simulate delays in the production of output values and the corresponding impact on the control function.

T-Res provides a custom block for representing the kernel and its scheduler. The block is configured with the selection of the scheduling policy and the behavior in case of deadline (period) overrun. The kernel block provides a set of activation signals as output. These activation signals go to instances of the the second type of custom blocks, representing tasks. Each task receives an activation signal from the kernel (indicating when the task begins or resumes execution), and is characterized by an execution time estimate (a configuration parameter), and a signal going back to the kenel and providing the amount of time that is still required by the task at each point in time. The task block produces as output a set of activation and latch signals for all the functional subsystems that are executed by the task.

With respect to the activation, sporadic tasks are characterized by an activation event going as input to the kernel block, or a periodic activation specification, provided as a configuration parameter to the kernel (for details, refer to [2]). The execution time description is provided to the kernel for each task using a simple language.

Figure 1. The TRes cosimulation architecture.

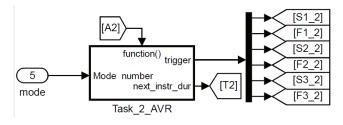

For the purpose of this project we entended the task model block and the timing information associated with it to allow for the modeling of the AVR behavior, as shown in Figure 2. The task block in T-Res includes a signal for the explicit activation in case of event-triggered tasks. This signal is used to define the activation of the task in correspondence to given angular positions of the engine crankshaft. In addition, the block has been extended to include another imput that refers to a *mode* index. This input can be used for multiple purposes and defines a different execution time behavior for a finite and enumerated set of conditions.

Figure 2. A custom block for modeling an AVR task.

In the case of AVR tasks, the mode index is provided from a simple block that looks at the engine rotation speeds and, based on the speed range, defines the execution time that the task requires.

The task will have different execution times for different speed modes according to a specification of execution times as a function of the mode (speed) index provided as a workspace variable.

# IV. SIMULINK MODELS OF THE ENGINE AND THE CONTROL TASKS

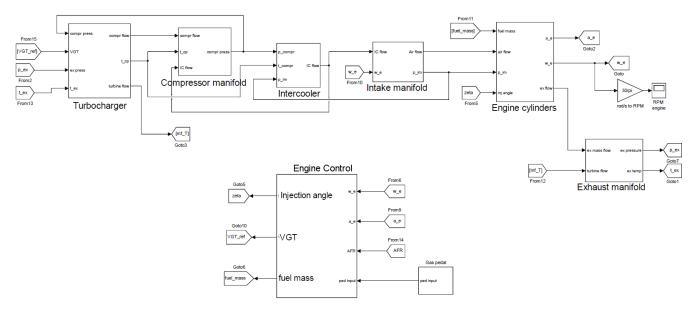

Figure 3 shows the model of the engine and the control functionality in Simulink. The blocks in the upper part of the figure represent the engine subsystems that are currently considered and includes the turbocharger, the compressor manifold, the intercooler, the intake and exhaust manifolds and the model of the engine cylinders. The subsystem on the bottom part of the figure wraps our model of the engine controller, with its outputs: the injection angle and duration and the VGT.

Figure 4 shows the subsystems realizing the controller functions and the task model of the controller. The model consists of a kernel (top left side), and four tasks on the bottom left side. One of the four tasks is an AVR, two are periodic and one represents background computations. The chains of subsystems on the right side represent the control functions implemented by the tasks. The second from the top contains the six subsystems that are executed by the AVR task (matching the six output signals from the AVR task block).

# V. OBJECTIVE AND STATUS

A detailed modeling of the control function is necessary to better understand the impact of deadline misses or long latencies. Depending on the implementation of the control function, a deadline miss may result in a late actuation, or a missed actuation or even an actuation with old data. In our controls implementation, the AVR task computes the phase and duration of the injection and passes them to the task that simulates the injection actuators. Hence, a missed deadline results in actuating the injectors with the values computed in the previous cycle with a likely error in phase and duration with respect to the ideal values.

The objective of our framework is multifold:

- To understand the effect of the scheduling on the engine performance and to use the environment for analyzing the impact of scheduling policies and parameters, such as evaluating fixed priority vs EDF or different possible priority assignments and task configurations.

- To analyze the timing parameters that truly of interest for evaluating the performance of the engine and possibly attept a characterization that isolates the attributes of interest. This includes, among others, the evaluation of schemes like m-k deadline misses, or overload management (maximum lateness).

To better characterize the design problem consisting in the optimal selection of the transition speeds for AVR tasks.

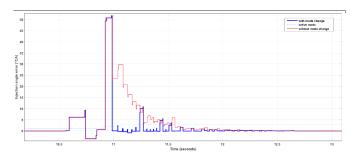

Currently, within the assumptions of our model, the simulation is able to show how the scheduling delays result in errors in the angle/duration of the injection actuation. Figure 5 shows preliminary results. In the figure graph, the vertical axis shows the phase error in the actuation of the injection for a sample manoeuvre consisting of a sudden acceleration and a corresponding increase in the engine rotation speed from low to high values. Two graphs are plotted in the figure. The graph in red (lighter) color shows the angle error when the execution time of the AVR task is kept constant, regardless of the engine speed. At high rotations, the task misses deadlines and the injection angle error grows to almost 50 degrees. When the execution time of the AVR task is reduced at high rates, the scheduling delays are much lower and, correspondingly, the angle error of the injection is much lower, as shown by the blue line in the graph. The angular error in the injection is related to a variation (loss) in the power performance of the engine.

Our objective is to relate the errors in phase and duration of the injection to a possible loss of power, providing ways to analyze the impact of scheduling with respect to the first performance function of interest. However, even within the limited scope of power performance analysis, the evaluation of the scheduling impact (and the AVR characteristics of tasks), requires that the model includes multiple representations of the control functionality, one for each possible execution mode of the AVR tasks. When these are available, the model will provide an early capability of expressing the performance impact of control implementations at different levels of complexity (for variable execution times or WCETs). Clearly, this is only the initial objective, given that a realistic model should also include the characterization of pollution, noise and efficiency.

Figure 5. Angular error in the injection caused by scheduling delays of the AVR task: error with fixed execution times (red) and with adaptive excution (in blue).

### VI. RELATED WORK

The presentation of the task model in which engine control tasks are implemented with a variable computational requirements for increasing speeds is in [4],

These tasks are also referred to adaptive variable-rate (AVR). Analyzing the schedulability of tasks sets consisting

of both periodic and AVR tasks is a difficult problem that has been addressed by several authors under various simplifying assumptions, under both fixed priority scheduling [5]–[7] and Earliest Deadline First (EDF) [8]–[10]. Other authors proposed methods for computing the exact interference [11] and the exact response time [7] of AVR tasks under fixed priority scheduling. It has been shown [10] that, given the large range of possibile interarrival times of an AVR task, fixed priority scheduling is not the best choice for engine control systems since, while EDF exhibits a nearly optimal scheduling performance. Based on this fact, Apuzzo et al. [12] provided an operating system support for AVR tasks under the Erika Enterprise kernel [13].

All the papers considered above, however, focused on analyzing the schedulability of task sets consisting of periodic and AVR tasks, without any concern on engine performance. A performance-driven design approach has been addressed in [14] for finding the transition speeds that trigger the mode changes of an AVR task.

A very large number of projects target the evaluation of scheduling policies and the analysis of task implementations. A necessarily incomplete list includes Yartiss [15], ARTISST [16], Cheddar [17], and Stress [18].

Finally, TrueTime [19] is a *freeware*<sup>1</sup> Matlab/Simulink-based simulation tool that has been developed at Lund University since 1999. It provides models of multi-tasking real-time kernels and networks that can be used in simulation models for networked embedded control systems. TrueTime is used by many research groups worldwide to study the (simulated) impact of lateness and deadline misses on controls. In TrueTime, the model of task code is represented by *code functions* that are written in either Matlab or C++ code. Several research works investigate the consequences of computation (scheduling) and communication delays on controls. An overview on the subject can be found in [20].

# REFERENCES

- [1] L. Guzzella and C. H. Onder, Introduction to Modeling and Control of Internal Combustion Engine Systems. Springer-Verlag, 2010.

- [2] F. Cremona, M. Morelli, and M. D. Natale, "Tres: A modular representation of schedulers, tasks, and messages to control simulations in simulink," in *Proc. of the 31st ACM Symposium on Applied Computing (SAC 2016)*, Pisa, Italy, April 4-8, 2016.

- [3] L. Palopoli, G. Lipari, L. Abeni, M. D. Natale, P. Ancilotti, and F. Conticelli, "A tool for simulation and fast prototyping of embedded control systems," in *LCTES/OM*, S. Hong and S. Pande, Eds. ACM, 2001, pp. 73–81.

- [4] D. Buttle, "Real-time in the prime-time," in Keynote speech at the 24th Euromicro Conference on Real-Time Systems, Pisa, Italy, July 12, 2012.

- [5] J. Kim, K. Lakshmanan, and R. Rajkumar, "Rhythmic tasks: A new task model with continually varying periods for cyber-physical systems," in *Proc. of the Third IEEE/ACM Int. Conference on Cyber-Physical* Systems (ICCPS 2012), Beijing, China, April 2012, pp. 28–38.

- [6] R. I. Davis, T. Feld, V. Pollex, and F. Slomka, "Schedulability tests for tasks with variable rate-dependent behaviour under fixed priority scheduling," in *Proc. 20th IEEE Real-Time and Embedded Technology* and Applications Symposium, Berlin, Germany, April 2014.

<sup>&</sup>lt;sup>1</sup>http://www3.control.lth.se/truetime/LICENSE.txt

- [7] A. Biondi, M. D. Natale, and G. Buttazzo, "Response-time analysis for real-time tasks in engine control applications," in *Proceedings of the* 6th International Conference on Cyber-Physical Systems (ICCPS 2015), Seattle, Washington, USA, April 14-16, 2015.

- [8] G. Buttazzo, E. Bini, and D. Buttle, "Rate-adaptive tasks: Model, analysis, and design issues," in *Proc. of the Int. Conference on Design, Automation and Test in Europe (DATE 2014)*, Dresden, Germany, March 24-28, 2014.

- [9] A. Biondi and G. Buttazzo, "Engine control: Task modeling and analysis," in *Proc. of the International Conference on Design, Automation and Test in Europe (DATE 2015)*, Grenoble, France, March 9-13, 2015, pp. 525–530.

- [10] A. Biondi, G. Buttazzo, and S. Simoncelli, "Feasibility analysis of engine control tasks under EDF scheduling," in *Proc. of the 27th Euromicro Conference on Real-Time Systems (ECRTS 2015)*, Lund, Sweden, July 8-10, 2015.

- [11] A. Biondi, A. Melani, M. Marinoni, M. D. Natale, and G. Buttazzo, "Exact interference of adaptive variable-rate tasks under fixed-priority scheduling," in *Proceedings of the 26th Euromicro Conference on Real-Time Systems (ECRTS 2014)*, Madrid, Spain, July 8-11, 2014.

- [12] V. A. A. Biondi and G. Buttazzo, "OSEK-like kernel support for engine control applications under EDF scheduling," in *Proceedings of* the 22nd IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS 2016), Vienna, Austria, April 11-14, 2016.

- [13] "Erika enterprise: an OSEK compliant real-time kernel." [Online]. Available: http://erika.tuxfamily.org/drupal/

- [14] A. Biondi, M. D. Natale, and G. Buttazzo, "Performance-driven design of engine control tasks," in *Proceedings of the 7th International Conference on Cyber-Physical Systems (ICCPS 2016)*, Vienna, Austria, April 11-14, 2016.

- [15] Y. Chandarli, F. Fauberteau, D. Masson, S. Midonnet, M. Qamhieh et al., "Yartiss: A tool to visualize, test, compare and evaluate real-time scheduling algorithms," in Proceedings of the 3rd International Workshop on Analysis Tools and Methodologies for Embedded and Real-time Systems, 2012, pp. 21–26.

- [16] D. Decotigny and I. Puaut, "Artisst: an extensible and modular simulation tool for real-time systems," in *Object-Oriented Real-Time Distributed Computing*, 2002.(ISORC 2002). Proceedings. Fifth IEEE International Symposium on. IEEE, 2002, pp. 365–372.

- [17] F. Singhoff, J. Legrand, L. Nana, and L. Marcé, "Cheddar: a flexible real time scheduling framework," in ACM SIGAda Ada Letters, vol. 24, no. 4. ACM, 2004, pp. 1–8.

- [18] N. C. Audsley, A. Burns, M. F. Richardson, and A. J. Wellings, "Stress: A simulator for hard real-time systems," *Software: Practice and Experience*, vol. 24, no. 6, pp. 543–564, 1994.

- [19] A. Cervin, D. Henriksson, B. Lincoln, J. Eker, and K.-E. Årzén, "How does control timing affect performance?" *IEEE control systems magazine*, vol. 23, no. 3, pp. 16–30, 2003.

- [20] K. J. Astrom and B. Wittenmark, "Adaptive control," in *Prentice Hall*, 2016.

Figure 3. Engine control model in Simulink.

Figure 4. Task model in TRES.

# Model Interpretation for an AUTOSAR compliant Engine Control Function

Sakthivel Manikandan Sundharam

University of Luxembourg

FSTC/Lassy

6, rue Richard Coudenhove-Kalergi

L-1359 Luxembourg

sakthivel.sundharam@uni.lu

Sebastian Altmeyer University of Amsterdam CSA Group Science Park 904 1098XH Amsterdam altmeyer@uva.nl Nicolas Navet

University of Luxembourg

FSTC/Lassy

6, rue Richard Coudenhove-Kalergi

L-1359 Luxembourg

nicolas.navet@uni.lu

Abstract—Model-Based Development (MBD) is a common practice in the automotive industry to develop complex software, for instance, the control software for automotive engines, which are deployed on modern multi-core hardware architectures. Such an engine control system consists of different sub-systems, ranging from air system to the exhaust system. Each of these subsystems, again, consists of software functions which are necessary to read from the sensors and write to the actuators. In this setting MBD provides indispensable means to model and implement the desired functionality, and to validate the functional, the non-functional, and in particular the real-time behavior against the requirements. Current industrial practice in model-based development completely relies on generative MBD, i.e., code generation to bridge the gap between model and implementation. An alternative approach, although not yet used in the automotive domain is model interpretation, the direct interpretation of the design models using interpretation engine running on top of the hardware. In this paper, we present a case study to investigate the applicability of model interpretation, in contrast to code generation, for the development of engine control systems. To this end, we model an engine cooling system, specifically the calculation of the engine-coolant temperature, using interpreted model based development, and discuss the benefits and low-lights compared to the existing code-generation practice.

### I. Introduction

Model-Based Development (MBD), also frequently referred to as Model-Driven Engineering (MDE), denotes the use of models as the main artifacts to drive the development of systems. It has been profoundly reshaping and improving the design of software-intensive embedded systems specifically. Traditionally, model-driven development (based on code generation) is deployed in the automotive industry. Code generation is used to generate code from a higher level model and create a working application.

As mentioned in [4], Model-Based Development is being used for series development by a majority of the automotive companies. Especially in development phases i.e., system design and coding, the model-based design is used extensively. As mentioned in [7], this kind of MBD used by automotive suppliers and car manufacturers is called *generative MBD*, since code and other artifacts are automatically generated from the model.

The other fundamental approach to achieve applications from models is *interpreted MBD*. Interpreted MBD can be

seen as a set of platform independent models that are directly interpreted by an execution engine running on top of the hardware, with or without an operating system.

The fact that models can be directly executable helps a great deal as the development cycle time can be shortened; and there is no distortion between the model and what is executed. Though, to the best of our knowledge, the technique of model interpretation remains unexplored in the automotive domain, it can facilitate and speed up the development, deployment and timing verification of applications with real-time constraints running on potentially complex hardware platforms. Verification also can be done more easily as defects will be caught earlier in the process since there is no difference between the model and the executable program. In this paper, we present a case-study to evaluate how *interpreted MBD* can be applied to an automotive software development scenario.

This paper is structured as follows. In Section II, we explain the state of the industrial practice of automotive function development. Section III describes an AUTOSAR-compliant engine-coolant temperature calculation function used as casestudy. In Section IV, we discuss our modeling approach, and Section V presents the case study. Finally, Section VI summarizes the results and discusses the case study. Section VII concludes the paper.

### II. AUTOMOTIVE FUNCTION DEVELOPMENT - STATE OF THE PRACTICE

We explain the state-of-the-art of the development of an automotive function using an automotive engine management software system, which are commonly developed using a Model Based Development (MBD). The engine is controlled by an Electronic Control Unit (ECU) that contains engine functions for different sub-systems.

The requirements of the engine functions are specified in one of the Application Life-cycle Management (ALM) suites and traced until its realization as ECU. In ALM, different tools are integrated to develop and maintain the software. For example, IBM has an ALM suite called IBM Rational Team Concert (RTC) where Rational DOORS is the requirements management tool that captures all the functional and non-functional requirements. These requirements are analyzed further to design the engine function. Popular Model Based

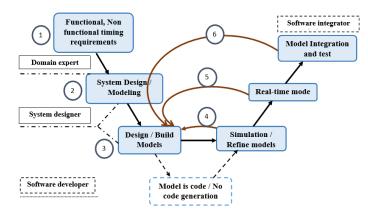

Fig. 1. Engine function development flow - Illustration of verification techniques, involved stakeholders and development phases.

Design (MBD) tools are MATLAB/Simulink (MLSL) from Mathworks, ASCET-MD from ETAS, and SCADE Suite from ANSYS. These industrial MBD tools further generate code for engine functions using code generators. Each engine control function is further (unit-) tested and integrated into the ECU.

Figure 1 shows the software function development flow practiced in the automotive industry. The system model of the engine captures the ideas and requirements. The model is an executable specification and can be simulated and rapid-prototyped to explore different design options. In the existing approach, the modeling environment is primarily used to describe the domain problem, in this case the engine function to be developed against the functional requirements. *Domain experts* and *software designers* are involved in this phase. The controller model is tested in a simulation environment (which includes the plant model, *i.e.* the engine) and this testing is called *Model-in-the-Loop* (MiL) testing to ensure that the model meets the requirements.

In the next step, the code is generated from the model using a code generator. Then, the code is verified under an engine model. This phase is referred to as *Software-in-the-Loop* (SiL) testing. *Software developers* are involved to test each engine function individually using unit testing. Next, the function is integrated with other existing engine functions in the integration phase by the *Software integrators*, typically a tier-one supplier. The complete engine software is then ported to the ECU hardware, which can be verified using a *Hardware-in-the-Loop* (HiL) testing system, such as PT-LABCAR, which realistically emulates vehicles I/Os.

In the current practice [3], the execution environment on the target is different from the execution within the modeling environment in terms of I/Os, scheduling and even in terms of generated code. Indeed, the target-generated code will be optimized towards the platform and thus be as efficient as possible. On the negative side, the build tool-chain must be available, and it takes a substantial amount of time to produce an executable program from the designed model (build time can require several 10s of minutes). Simulink and its block sets (like Simscape, Stateflow etc.) are examples for modeling environment and Embedded Coder is an example of the code generator for production code generation on a specific target processor. The generated code can be further customized to meet the requirements (e.g., with respect to safety). In the automotive software development, there is a high probability for mixed-mode development, where generated code is integrated with manually-developed functions.

### III. AUTOSAR-COMPLIANT ENGINE FUNCTION

The engine cooling system is an important part of the vehicle. It is responsible for maintaining optimum operating temperature. The coolant is circulated through the engine block with the help of an electric water pump. The coolant will reduce the temperature of the engine block and then will run through the radiator equipped with a fan to remove waste heat.

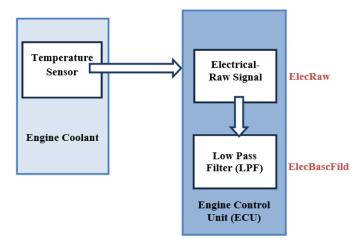

Fig. 2. Physical layout of an AUTOSAR compliant engine-coolant system function - Engine coolant temperature sensor connected to an ECU  $\,$

Figure 2 shows the physical layout of the engine-coolant temperature calculation which is considered as the use case to

present our modeling approach. The engine-coolant temperature sensor plays an indispensable role in the engine cooling system. Precise information about the temperature is essential due to various reasons: the data are used by the engine control unit to adjust the fuel injection and ignition timing. Further, the temperature value is used to control the cold starting of the engine, to control the calculation of the fuel quantity, and to control the fan speed of the electric cooling radiator. This data is also used to provide readings of the coolant temperature gauge to the dashboard to protect the engine from over-heating.

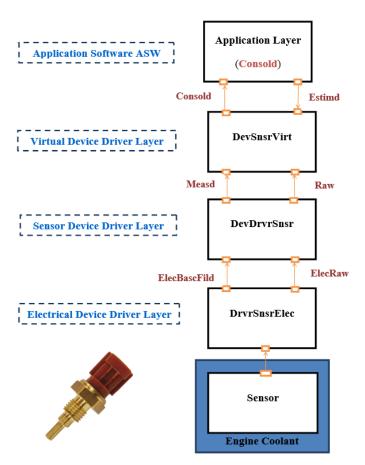

The engine-coolant temperature sensor is connected to the engine ECU through an analog to digital pin. The electrical output is obtained from the sensor that monitors the temperature of the engine-coolant. As per AUTOSAR design pattern [2] catalogue for standard sensors, the overall system consists of 3 modules as depicted in Figure 3. Sensor/Actuator Components are special AUTOSAR software components which encapsulate the dependencies of the application on specific sensors or actuators. The AUTOSAR architecture takes care of hiding the specifics of the micro-controller (this is done in the micro-controller abstraction layer, MCAL, part of the AUTOSAR infrastructure running on the ECU) and the ECU electronics (handled by the ECU-Abstraction layer, also part of the AUTOSAR Basic Software).

Fig. 3. AUTOSAR design pattern for a standard sensor

The architecture of the engine-coolant temperature calculation function involves 3 AUTOSAR software components:

# **Electrical Device Driver Layer (DrvrSnsrElec):**

The electrical value from the temperature sensor is read through the input pin and stored in the variable *ElecRaw*. The raw electrical signal (*ElecRaw*) is rugged against signal faults using the Low Pass Filter (*LPF*) and the filtered raw electrical signal (*ElecBascFild*) is obtained.

# Sensor Device Driver Layer (DevDrvrSnsr):

At this stage, the raw electrical signal is converted into its physical temperature value (*Raw*) using a lookup-table, where the corresponding value is provided. The temperature value of the filtered electrical signal (*ElecBascFild*) is also obtained from the lookup-table and is provided to the next layer.

# Virtual Device Driver Layer (DevSnsrVirt):

In this layer, the possible signal range check, electrical errors, cable interruption and sensor faults that may occur are identified. This is done in order that incorrect values from the sensor are not taken into account for the calculation in case of sensor malfunctioning. Other errors such as a cable interruption, short circuit to battery or sensor voltage saturation can also be detected and appropriate flags will be set:

- ElecBascFildbit The electrical validity bit shows that the sensor raw value is electrical valid.

- ElecBascFildbitCommon The common validity bit shows that the engine-coolant temperature as a whole is valid and can be transferred to the application Layer. Based on the temperature values calculated in this layer, the obtained temperature value (Measd) is compared with the estimated value (Estimd) from the application layer. This comparison determines the validity of the calculated value. If valid, the final temperature value (Consld) is sent to the application layer.

# IV. FUNCTION DEVELOPMENT - PROPOSED APPROACH

To the best of our knowledge, model interpretation for automotive function development has not been explored and experimented in the past. In case of model interpretation, a generic model-interpretation engine is implemented which executes the model of the engine function. As shown in Figure 4, the modeling environment includes the execution environment. Hence, the executable artifacts (*i.e.*, model and execution engine) are available within this environment. The model interpretation can be launched within the development environment or on a target platform. In the latter case, the interpretation can run on top of an OS or directly on the hardware. There are two possible interpretation modes: simulation and real-time. Simulation mode is suited for the use in the design phase, where execution should be as fast as possible, which implies that the activation frequencies of the processes

are not respected and they execute (conceptually) in zero time. Typically, executing in simulation mode is several orders of magnitude faster than in the real-time mode. Real-time mode is for the execution of the program with the actual desired temporal behavior of the application.

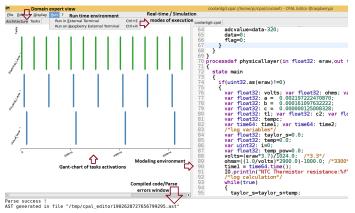

Fig. 4. An integrated environment, here the CPAL-Editor, with the code of the model, the Gantt chart of the processes activations and the possibility to execute the models in simulation and real-time mode both locally or on a target.

To ensure that simulation reflects the real-time behavior on the target platform, timing annotations (e.g., execution time latencies, jitters, etc) can be introduced in simulation mode. Those timing annotations can be derived from measurements on the target architecture, from WCET analysis and, possibly, by schedulability analysis if other software components can interfere with the function under development. Timing accurate simulation thus provides benefits to identify faults in design phase itself, earlier, thus than with the traditional design process.

As the model itself can be executed, no additional artifacts are needed, and, unlike in the traditional generative MBD, no target specific code is generated. Instead, the specifics of the platform are taken care by the interpretation engine. Further steps of the application development, such as compilation of source code to object code and the linking stage to produce the executable program, are not required.

### V. A Case Study - Engine-coolant temperature calculation

The model of the engine-coolant system is developed in the CPAL (Cyber Physical Action Language, see [1, 6]), which is a new language to model, simulate, verify and program Cyber Physical Systems. CPAL<sup>1</sup> is a language jointly developed by our research group at the University of Luxembourg and the company RTaW. Many industrial use-cases are demonstrated [5] using CPAL in the past.

The model-based environment of CPAL consists of a single integrated development environment, i.e., the CPAL-Editor. The CPAL editor, combines the design, simulation, execution

(both locally and on a target), visualization of the functional architecture and execution chronogram in one integrated environment. The model-interpretation engine is specific to the target platform. This interpretation engine can be executed on top of an operating system or without an operating system, the latter being called Bare-Metal Model Interpretation (BMMI). CPAL BMMI is available on the NXP Semiconductors Freedom-K64F, a low-cost development platform which is form-factor compatible with the Arduino R3 pin layout. The experiments in this study are performed on a Raspberry Pi equipped with a multi-core ARM Cortex-A7 processor operating at 900 MHz running Raspbian OS.

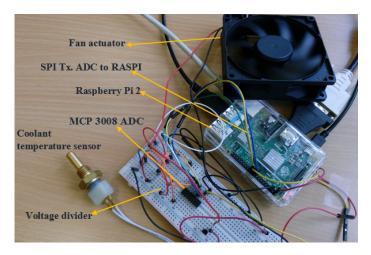

A typical engine-coolant temperature sensor can measure in the range -40°C to +150°C. In our case study, we have considered a Negative Temperature Coefficient (NTC) type sensor with an operating voltage as 3.3V. Figure 5 shows the experimental setup which aims to mimic the engine cooling system. The MCP3008 is an external ADC interface which is connected to the sensor. Since the sensor operates with the thermistor principle, a voltage divider circuit with 3.3V reference is added. ADC data from MCP3008 is communicated to the processor using the Serial Peripheral Interface (SPI). The sensor software component is modeled according to the AUTOSAR design catalog described in Section III. The speed of the electric fan is controlled based on the measured temperature.

Fig. 5. Experimental set-up - Sensor interfacing to hardware

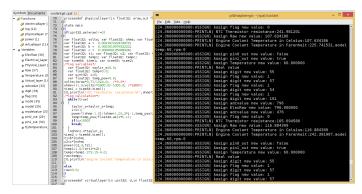

Out of the two possible CPAL execution environments (*i.e.*, bare-metal or hosted by an OS), we use the interpretation engine on top of an OS (Raspbian on Raspberry Pi) which can also execute in real-time, although with a lesser real-time predictability than the bare-metal implementation. The engine-coolant temperature is calculated by the sensor software component modeled in CPAL. Figure 6 shows the sample run-time environment where simulation and real-time execution are performed. Both interactive and non-interactive executions are possible. The interactive mode of execution is useful in program analysis and debugging. In interactive mode, the user has different execution options, such as a step-by-

<sup>&</sup>lt;sup>1</sup>The CPAL documentation, graphical editor and the execution engine for Windows, Linux and Raspberry Pi platforms are freely available from http://www.designcps.com.

step execution, or uninterrupted execution for a pre-defined duration.

Fig. 6. CPAL model and execution environment under real-time mode

Since it is an interpretation-based execution environment, the user can list and change the values of global variables at run-time, as well as execute additional code statements. In non-interactive mode, the program is executed indefinitely or for a specified duration without requiring additional user inputs.

### VI. RESULTS AND DISCUSSIONS

From the case-study experience, we present our proposed development flow for function development. Figure 7 shows the development flow of model interpreted approach to develop an engine function.

Fig. 7. Model interpreted engine function development flow - steps and stakeholders involved

a) Model interpreted development steps: In the first step all functional, non-functional including timing requirements of the engine function are collected. These are further analyzed by domain experts. The specifications are implemented in CPAL (step 2 - system design in Figure 7). During the development, as soon as the function model is updated the functional architecture, and other views created out of the model such as execution Gantt charts, are automatically updated too (step 3) which is done in the background along with the modifications. This allows the designer to immediately visualize and understand the effects of the changes made,

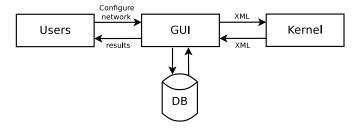

without the need for building the executable and running it in debug mode. The latest version of the model is always available to execute, be it in simulation mode or real-time mode, locally or on a target. Typically performed once the simulation is satisfactory (step 4), the execution in real-time mode (step 5) helps the designer to assess the performances on the target, enabling rapid-prototyping. If simulation or execution in real-time mode highlights faults, the model is refined in an iterative process. From the development of the engine-coolant temperature calculation function, we here summarize the benefits and differences against the existing generative MBD approach.